# **OPEN** Industry Standard, Flexible Architecture

**GREEN**

Less Heat, Less Power Consumption

**STABLE**

Stable and Reliable Solution

## ver/Workstation

## TURIN2D24G-2L+ GENOA2D24G-2L+

User Manual

Version 2.00

Published Nov. 2024

Copyright@2024 ASRock Rack INC. All rights reserved.

#### Copyright Notice:

No part of this documentation may be reproduced, transcribed, transmitted, or translated in any language, in any form or by any means, except duplication of documentation by the purchaser for backup purpose, without written consent of ASRock Rack Inc.

Products and corporate names appearing in this documentation may or may not be registered trademarks or copyrights of their respective companies, and are used only for identification or explanation and to the owners' benefit, without intent to infringe.

#### Disclaimer:

Specifications and information contained in this documentation are furnished for informational use only and subject to change without notice, and should not be constructed as a commitment by ASRock Rack. ASRock Rack assumes no responsibility for any errors or omissions that may appear in this documentation.

With respect to the contents of this documentation, ASRock Rack does not provide warranty of any kind, either expressed or implied, including but not limited to the implied warranties or conditions of merchantability or fitness for a particular purpose.

In no event shall ASRock Rack, its directors, officers, employees, or agents be liable for any indirect, special, incidental, or consequential damages (including damages for loss of profits, loss of business, loss of data, interruption of business and the like), even if ASRock Rack has been advised of the possibility of such damages arising from any defect or error in the documentation or product.

#### ASRock Rack's Website: www.ASRockRack.com

#### CALIFORNIA, USA ONLY

The Lithium battery adopted on this motherboard contains Perchlorate, a toxic substance controlled in Perchlorate Best Management Practices (BMP) regulations passed by the California Legislature. When you discard the Lithium battery in California, USA, please follow the related regulations in advance.

"Perchlorate Material-special handling may apply, see <a href="www.dtsc.ca.gov/hazardouswaste/">www.dtsc.ca.gov/hazardouswaste/</a> perchlorate"

#### **AUSTRALIA ONLY**

Our goods come with guarantees that cannot be excluded under the Australian Consumer Law. You are entitled to a replacement or refund for a major failure and compensation for any other reasonably foreseeable loss or damage caused by our goods. You are also entitled to have the goods repaired or replaced if the goods fail to be of acceptable quality and the failure does not amount to a major failure. If you require assistance please call ASRock Rack Tel: +886-2-55599600 ext.123 (Standard International call charges apply)

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

## UK CA

ASRock Rack INC. hereby declares that this device is in compliance with the essential requirements and other relevant provisions of related UKCA Directives. Full text of UKCA declaration of conformity is available at: http://www.asrockrack.com

ASRock Rack INC. hereby declares that this device is in compliance with the essential requirements and other relevant provisions of related Directives. Full text of EU declaration of conformity is available at: http://www.asrockrack.com

ASRock Rack follows the green design concept to design and manufacture our products, and makes sure that each stage of the product life cycle of ASRock Rack product is in line with global environmental regulations. In addition, ASRock Rack disclose the relevant information based on regulation requirements.

Please refer to <a href="https://www.asrockrack.com/general/about.asp?cat=Responsibility">https://www.asrockrack.com/general/about.asp?cat=Responsibility</a> for information disclosure based on regulation requirements ASRock Rack is complied with:

DO NOT throw the motherboard in municipal waste. This product has been designed to enable proper reuse of parts and recycling. This symbol of the crossed out wheeled bin indicates that the product (electrical and electronic equipment) should not be placed in municipal waste. Check local regulations for disposal of electronic products.

#### Contents

| Chap  | oter 1 Introduction                   | 1  |

|-------|---------------------------------------|----|

| 1.1   | Package Contents                      | 1  |

| 1.2   | Specifications                        | 2  |

| 1.3   | Unique Features                       | 6  |

| 1.4   | Motherboard Layout                    | 7  |

| 1.5   | Onboard LED Indicators                | 11 |

| 1.6   | I/O Panel                             | 12 |

| 1.7   | Block Diagram                         | 14 |

| Chap  | oter 2 Installation                   | 15 |

| 2.1   | Screw Holes                           | 15 |

| 2.2   | Pre-installation Precautions          | 15 |

| 2.3   | Installing the CPU                    | 16 |

| 2.4   | Installation of Memory Modules (DIMM) | 21 |

| 2.5   | Jumper Setup                          | 23 |

| 2.6   | Onboard Headers and Connectors        | 24 |

| 2.7   | ATX PSU Power Connections             | 52 |

| 2.8   | Dr. Debug                             | 53 |

| 2.9   | Identification purpose LED/Switch     | 59 |

| 2.10  | Dual LAN and Teaming Operation Guide  | 60 |

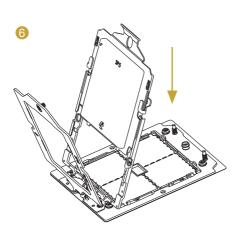

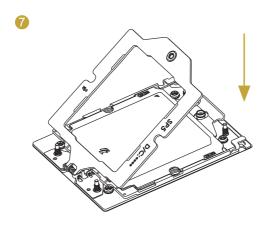

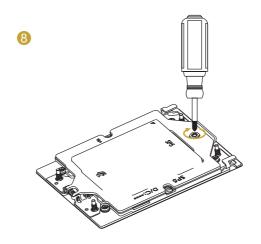

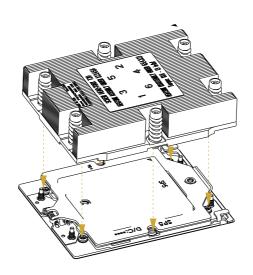

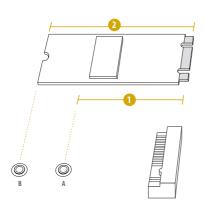

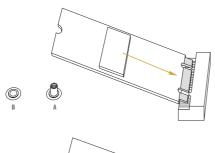

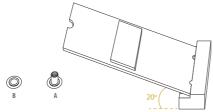

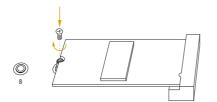

| 2.11  | M.2 SSD Module Installation Guide     | 61 |

| Chap  | oter 3 UEFI Setup Utility             | 63 |

| 3.1   | Introduction                          | 63 |

| 3.1.1 | UEFI Menu Bar                         | 63 |

| 3.1.2  | Navigation Keys                 | 64 |

|--------|---------------------------------|----|

| 3.2    | Main Screen                     | 65 |

| 3.2.1  | Mother Board Information        | 66 |

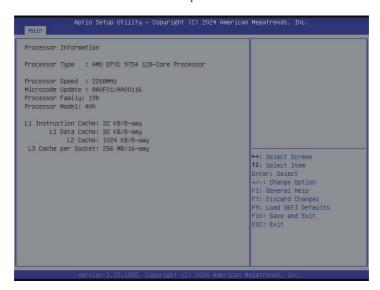

| 3.2.2  | Processor Information           | 66 |

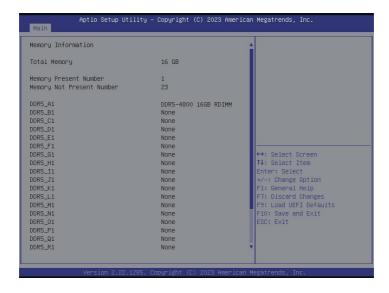

| 3.2.3  | Memory Information              | 67 |

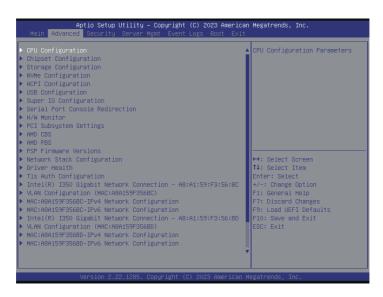

| 3.3    | Advanced Screen                 | 68 |

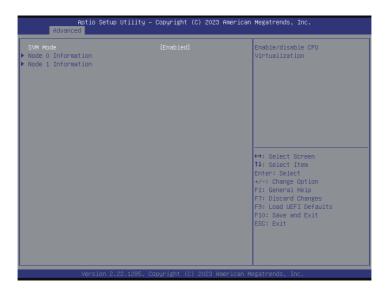

| 3.3.1  | CPU Configuration               | 69 |

| 3.3.2  | Chipset Configuration           | 70 |

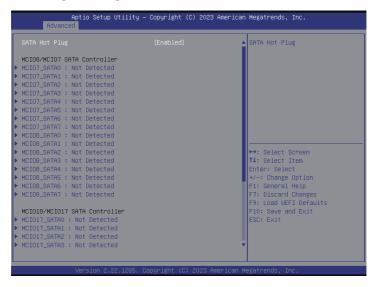

| 3.3.3  | Storage Configuration           | 72 |

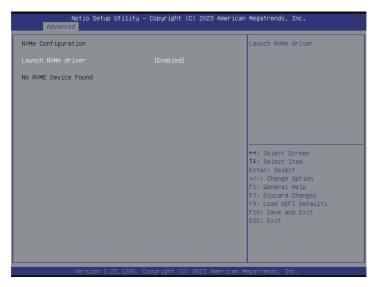

| 3.3.4  | NVMe Configuration              | 73 |

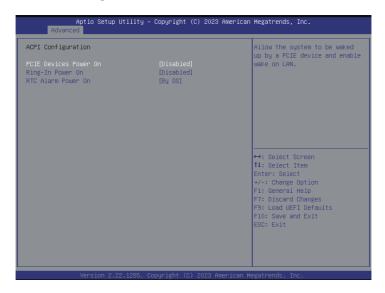

| 3.3.5  | ACPI Configuration              | 74 |

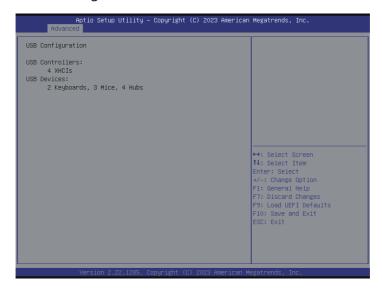

| 3.3.6  | USB Configuration               | 75 |

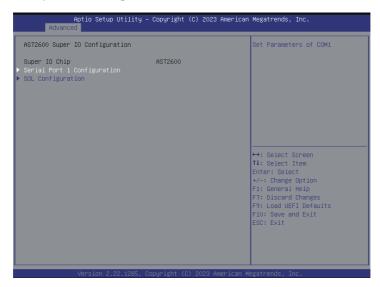

| 3.3.7  | Super IO Configuration          | 76 |

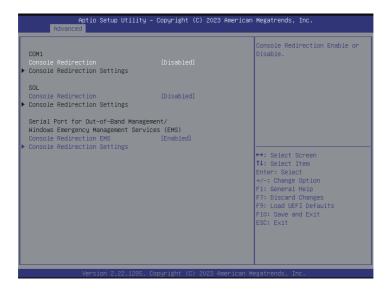

| 3.3.8  | Serial Port Console Redirection | 77 |

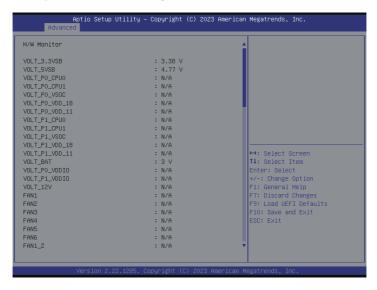

| 3.3.9  | H/W Monitor                     | 80 |

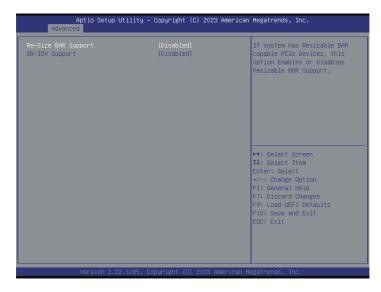

| 3.3.10 | PCI Subsystem Settings          | 81 |

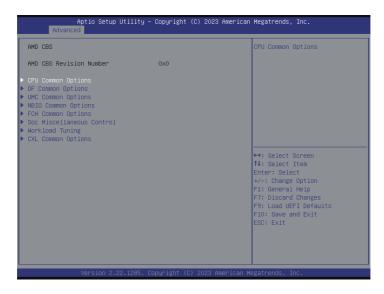

| 3.3.11 | AMD CBS                         | 82 |

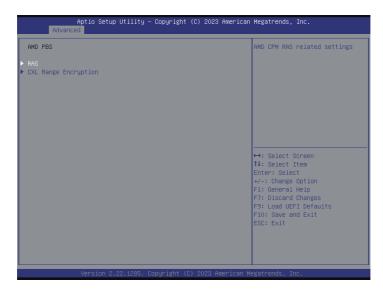

| 3.3.12 | AMD PBS                         | 83 |

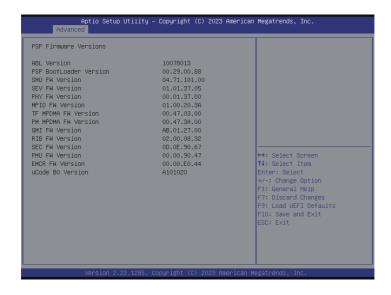

| 3.3.13 | PSP Firmware Versions           | 85 |

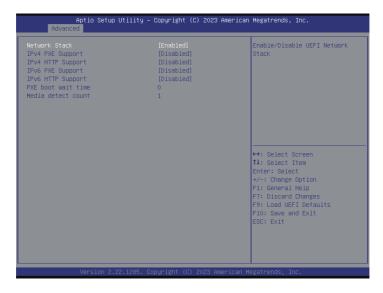

| 3.3.14 | Network Stack Configuration     | 86 |

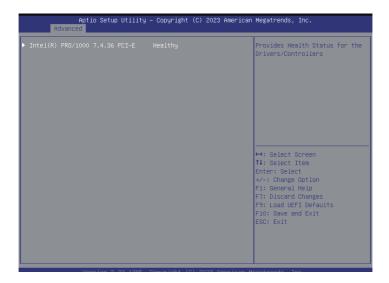

| 3.3.15 | Driver Health                   | 88 |

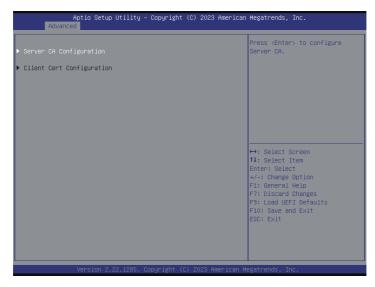

| 3.3.16 | Tls Auth Configuration          | 89 |

| 3.3.17 | Instant Flash                   | 90 |

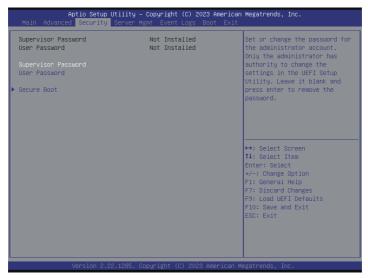

| 3.4    | Security                        | 91 |

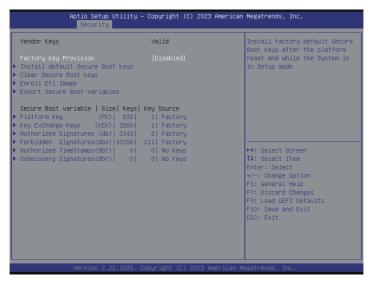

| 3.4.1                            | Key Management                                                                                                            | 93                              |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

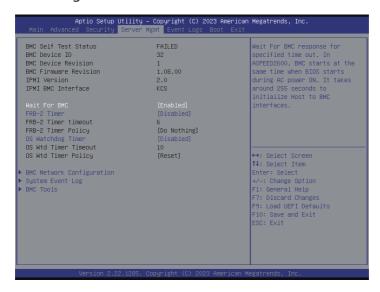

| 3.5                              | Server Mgmt                                                                                                               | 97                              |  |

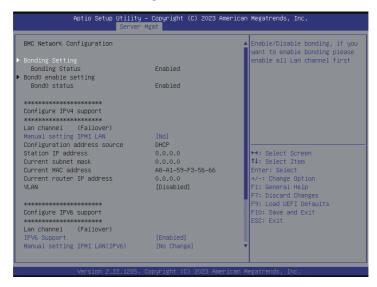

| 3.5.1                            | BMC Network Configuration                                                                                                 | 99                              |  |

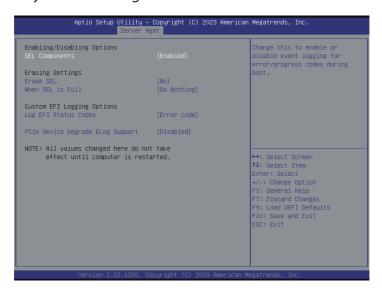

| 3.5.2                            | System Event Log                                                                                                          | 101                             |  |

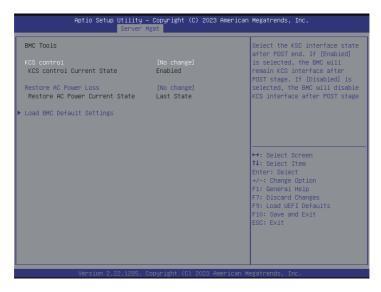

| 3.5.3                            | BMC Tools                                                                                                                 | 102                             |  |

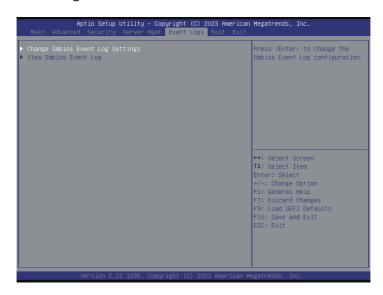

| 3.6                              | Event Logs                                                                                                                | 103                             |  |

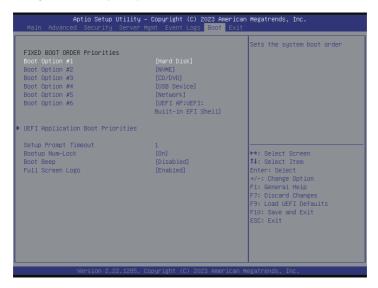

| 3.7                              | Boot Screen                                                                                                               | 105                             |  |

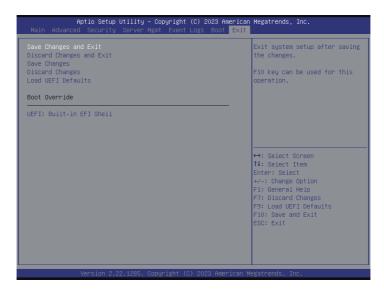

| 3.8                              | Exit Screen                                                                                                               | 106                             |  |

| Chan                             | ter 4 Software Support                                                                                                    | 107                             |  |

| Citap                            | ter i sortifare support                                                                                                   | 107                             |  |

| 4.1                              | Download and Install Operating System                                                                                     | 107                             |  |

| ·                                | • •                                                                                                                       |                                 |  |

| 4.1                              | Download and Install Operating System                                                                                     | 107                             |  |

| 4.1<br>4.2<br>4.3                | Download and Install Operating System  Download and Install Software Drivers                                              | 107<br>107                      |  |

| 4.1<br>4.2<br>4.3                | Download and Install Operating System  Download and Install Software Drivers  Contact Information                         | 107<br>107<br>107               |  |

| 4.1<br>4.2<br>4.3<br><b>Chap</b> | Download and Install Operating System  Download and Install Software Drivers  Contact Information  oter 5 Troubleshooting | 107<br>107<br>107<br><b>108</b> |  |

## **Chapter 1 Introduction**

Thank you for purchasing ASRock Rack *TURIN2D24G-2L+ / GENOA2D24G-2L+* motherboard, a reliable motherboard produced under ASRock Rack's consistently stringent quality control. It delivers excellent performance with robust design conforming to ASRock Rack's commitment to quality and endurance.

In this manual, chapter 1 and 2 contains introduction of the motherboard and step-by-step guide to the hardware installation. Chapter 3 and 4 contains the configuration guide to BIOS setup and information of the Sofware Support.

Because the motherboard specifications and the BIOS software might be updated, the content of this manual will be subject to change without notice. In case any modifications of this manual occur, the updated version will be available on ASRock Rack website without further notice. Find the latest memory and CPU support lists on ASRock Rack website as well. ASRock Rack's Website: <a href="https://www.ASRockRack.com">www.ASRockRack.com</a>

For any technical supports, please visit the website for specific information about the using model. <a href="http://www.asrockrack.com/support/">http://www.asrockrack.com/support/</a>

#### 1.1 Package Contents

- ASRock Rack TURIN2D24G-2L+ / GENOA2D24G-2L+ motherboard (Proprietary form factor: 16.9" x 13.8", 42.9cm x 35.1cm)

- · Quick installation guide

- 1 x ATX 4P to 24P power cable (8cm)

- 2 x screws for M.2 sockets

If any items are missing or appear damaged, contact the authorized dealer.

## 1.2 Specifications

| TURIN2D24G-2L+ / GENOA2D24G-2L+                         |                                                                     |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Physical Status                                         |                                                                     |  |  |

| Form Factor                                             | n Factor Proprietary                                                |  |  |

| Dimension                                               | 16.9" x13.8"                                                        |  |  |

| Processor System                                        |                                                                     |  |  |

| CPU                                                     | Supports AMD EPYC™ 9005*/9004 (with AMD 3D V-Cache™                 |  |  |

|                                                         | Technology) and 97x4 series processors                              |  |  |

| *For GENOA2D24G-2L+, a                                  | BIOS update is required to support AMD EPYC™ 9005 series processors |  |  |

| Socket                                                  | Dual Socket SP5 (LGA6096)                                           |  |  |

| Thermal Design                                          | GENOA2D24G-2L+:                                                     |  |  |

| Power (TDP)                                             | Up to 400W                                                          |  |  |

|                                                         | TURIN2D24G-2L+:                                                     |  |  |

|                                                         | Up to 500W                                                          |  |  |

| Chipset                                                 | System on Chip                                                      |  |  |

| System Memory                                           |                                                                     |  |  |

| Supported DIMM                                          | 12+12 DIMM slots (1DPC)                                             |  |  |

| Quantity                                                |                                                                     |  |  |

| Supported Type                                          | Supports DDR5 288-pin RDIMM, RDIMM-3DS                              |  |  |

| Max. Capacity per                                       | RDIMM: up to 96GB (2R)                                              |  |  |

| DIMM 3DS RDIMM: up to 512GB (2S8RX4)                    |                                                                     |  |  |

| Max. Frequency GENOA2D24G-2L+:                          |                                                                     |  |  |

|                                                         | 4800MHz                                                             |  |  |

|                                                         | TURIN2D24G-2L+:                                                     |  |  |

|                                                         | 6000MHz (For EPYC 9005 series processors)                           |  |  |

|                                                         | 4800MHz (For EPYC 9004 series processors)                           |  |  |

| Voltage                                                 | 1.1V                                                                |  |  |

| Note                                                    | Memory capacity, frequency, or voltage support is to be validated   |  |  |

| SATA/SAS Storage                                        |                                                                     |  |  |

| CPU Built-in Storage                                    | AMD EPYC <sup>™</sup> 9005/9004 (Up to 32 SATA 6Gb/s):              |  |  |

|                                                         | 4 MCIO                                                              |  |  |

| Additional SATA                                         | ASM1061 (2 SATA 6Gb/s):                                             |  |  |

| Controller                                              | 2 M.2                                                               |  |  |

| Ethernet                                                |                                                                     |  |  |

| Additional GbE                                          | Intel® i350: 2 RJ45 (1GbE)                                          |  |  |

| Controller                                              |                                                                     |  |  |

| Other PCIe Expansion                                    | Connectors                                                          |  |  |

| M.2 Slot M2_1 (PCIe3.0 x4 or SATA 6Gb/s), supports 2280 |                                                                     |  |  |

| M.2 Slot                                                | W12_1 (PC163.0 x4 of SATA 0G0/8), supports 2200/22110 form          |  |  |

| M.2 Slot                                                | factor [CPU0]                                                       |  |  |

| M.2 Slot                                                |                                                                     |  |  |

| MCIO | GENOA2D24G-2L+:                                     |

|------|-----------------------------------------------------|

|      | 6 MCIO (PCIe5.0 / CXL1.1 x8) [CPU0]                 |

|      | 2 MCIO (PCIe5.0 / CXL1.1 x8 or 8 SATA 6Gb/s) [CPU0] |

|      | 2 MCIO (PCIe5.0 x8 or 8 SATA 6Gb/s) [CPU0]*         |

|      | 6 MCIO (PCIe5.0 / CXL1.1 x8) [CPU1]                 |

|      | 2 MCIO (PCIe5.0 / CXL1.1 x8 or 8 SATA 6Gb/s) [CPU1] |

|      | 2 MCIO (PCIe5.0 x8) [CPU1]                          |

|      | TURIN2D24G-2L+:                                     |

|      | 6 MCIO (PCIe5.0 / CXL2.0 x8) [CPU0]                 |

|      | 2 MCIO (PCIe5.0 / CXL2.0 x8 or 8 SATA 6Gb/s) [CPU0] |

|      | 2 MCIO (PCIe5.0 x8 or 8 SATA 6Gb/s) [CPU0]*         |

|      | 6 MCIO (PCIe5.0 / CXL2.0 x8) [CPU1]                 |

|      | 2 MCIO (PCIe5.0 / CXL2.0 x8 or 8 SATA 6Gb/s) [CPU1] |

|      | 2 MCIO (PCIe5.0 x8) [CPU1]                          |

\*MCIO9, 10 support PCIe only while installing 2 processors

| MC109, 10 support PCIe only while installing 2 processors |                                                        |  |  |

|-----------------------------------------------------------|--------------------------------------------------------|--|--|

| Server Management                                         |                                                        |  |  |

| BMC Controller ASPEED AST2600                             |                                                        |  |  |

| IPMI Dedicated                                            | 1 Realtek RTL8211F for dedicated management GLAN       |  |  |

| GLAN                                                      |                                                        |  |  |

| Graphics                                                  |                                                        |  |  |

| Controller                                                | ASPEED AST2600                                         |  |  |

| VRAM                                                      | DDR4 512MB                                             |  |  |

| Security                                                  |                                                        |  |  |

| TPM                                                       | 1 (13-pin, SPI)                                        |  |  |

| Rear I/O                                                  |                                                        |  |  |

| UID Button/LED                                            | 1 UID button w/ LED                                    |  |  |

| Other Button/LED                                          | 1 PWR button, 1 RST button, 1 NMI button, 1 HDD LED, 1 |  |  |

|                                                           | SYS LED                                                |  |  |

| VGA Port                                                  | 1 DB15 (VGA)                                           |  |  |

| USB                                                       | 4 Type-A (USB3.2 Gen1)                                 |  |  |

| RJ45                                                      | 2 RJ45 (1GbE), 1 dedicated IPMI                        |  |  |

| Hardware Monitor                                          |                                                        |  |  |

| Temperature                                               | CPU, MB, Card side Temperature Sensing                 |  |  |

| Fan                                                       | Fan Tachometer                                         |  |  |

|                                                           | CPU Quiet Fan (Allow Chassis Fan Speed Auto-Adjust by  |  |  |

|                                                           | CPU Temperature)                                       |  |  |

|                                                           | Fan Multi-Speed Control                                |  |  |

| Voltage                                                   | P0_VDDCR_CPU0, P0_VDDCR_CPU1, P0_VDDCR_SOC,            |  |  |

| -                                                         | P0_VDD_18_DUAL, P0_VDD_11_S3, P0_VDDIO, P1_            |  |  |

|                                                           | VDDCR_CPU0, P1_VDDCR_CPU1, P1_VDDCR_SOC, P1_           |  |  |

|                                                           | VDD_18_DUAL, P1_VDD_11_S3, P1_VDDIO, +BAT, +12V,       |  |  |

|                                                           | +3VSB, +5VSB                                           |  |  |

|                                                           | 1 '                                                    |  |  |

| System BIOS           |                                                              |

|-----------------------|--------------------------------------------------------------|

| Type                  | AMI UEFI BIOS; 256 Mb (32MB) SPI Flash ROM                   |

| Features              | ASRock Rack Instant Flash, ACPI 6.4 and about compliance     |

|                       | wake up events, SMBIOS 3.5.0 and above, Plug and Play(PnP)   |

| Internal Connectors/H |                                                              |

| PSU Connector         | 6 Micro-Hi (8-pin, ATX 12V), 1 Micro-Fit (4-pin, ATX PSU     |

| Toe commenter         | signal) w/ ATX 24-pin adapter cable, 1 (2-pin, +5V)          |

| Auxiliary Panel       | 1 (18-pin): chassis intrusion, system fault LED, LAN1/LAN2   |

| Header                | activity LED, locate, SMBus                                  |

| System Panel Header   | 1 (9-pin): power switch, reset switch, system power LED,     |

|                       | HDD activity LED                                             |

| NMI Button            | 1                                                            |

| COM Header            | 1                                                            |

| VGA Header            | 1                                                            |

| Fan Header            | 6 (6-pin)                                                    |

| TPM Header            | 1 (13-pin,SPI)                                               |

| SGPIO Header          | 6                                                            |

| HSBP                  | 1                                                            |

| SMbus Header          | 4                                                            |

| PMbus Header          | 1                                                            |

| IPMB Header           | 1                                                            |

| Clear CMOS            | 1 (contact pads)                                             |

| USB 3.2 (Gen1)        | 2 (19-pin, 2 USB3.2 Gen1)                                    |

| Header                |                                                              |

| LED Indicators        |                                                              |

| Standby Power LED     | 1 (5VSB)                                                     |

| 80 Debug Port LED     | 1                                                            |

| Fan Fail LED          | 6                                                            |

| BMC Heartbeat LED     | 1                                                            |

| Support OS            |                                                              |

| OS                    | Microsoft® Windows®:                                         |

|                       | - Server 2019 (64bit)                                        |

|                       | - Server 2022 (64bit)                                        |

|                       | - Server 2025 (64bit)                                        |

|                       | Linux*:                                                      |

|                       | - RedHat Enterprise Linux Server 8.10 (64bit) / Server 9.5   |

|                       | (64bit)                                                      |

|                       | - SUSE SLES 15.5(64bit) / 15.6(64bit)                        |

|                       | - UBuntu 22.04.5 (64bit) / 24.04 (64bit)                     |

|                       | Hypervisor                                                   |

|                       | Hypervisor: - VMWare ESXi / 8.0 U3 / 9.0                     |

|                       | - VIVI VV arc LOXI / 0.0 OJ / 7.0                            |

|                       | *Please refer to the website for the latest OS support list. |

| Enviroment    |                            |  |

|---------------|----------------------------|--|

| Operating     | 10 - 35°C (50 - 95degF)    |  |

| temperature   |                            |  |

| Non-operating | -40 - 70°C (-40 - 158degF) |  |

| temperature   |                            |  |

NOTE: Please refer to the website for the latest specifications.

This motherboard supports Wake from on Board LAN. To use this function, please make sure that the "Wake on Magic Packet from power off state" is enabled in Device Manager > Intel\* Ethernet Connection > Power Management. And the "PCI Devices Power On" is enabled in UEFI SETUP UTILITY > Advanced > ACPI Configuration. After that, onboard LAN1&2 can wake up S5 under OS.

If installing Intel® LAN utility or Marvell SATA utility, this motherboard may fail Windows® Hardware Quality Lab (WHQL) certification tests. If installing the drivers only, it will pass the WHQL tests.

#### 1.3 Unique Features

ASRock Rack Instant Flash is a BIOS flash utility embedded in Flash ROM. This convenient BIOS update tool allows user to update system BIOS without entering operating systems first like MS-DOS or Windows. With this utility, press the <F6> key during the POST or the <F2> key to enter into the BIOS setup menu to access ASRock Rack Instant Flash. Just launch this tool and save the new BIOS file to the USB flash drive, floppy disk or hard drive, then updating the BIOS only in a few clicks without preparing an additional floppy diskette or other complicated flash utility. Please be noted that the USB flash drive or hard drive must use FAT32/16/12 file system.

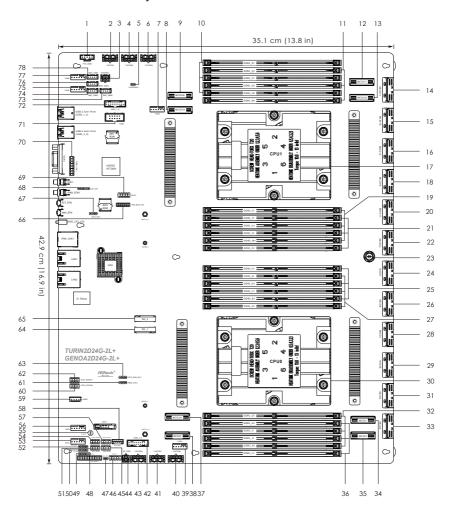

### 1.4 Motherboard Layout

| No. | Description                                              |

|-----|----------------------------------------------------------|

| 1   | PSU SMBus Header (PSU_SMB1)                              |

| 2   | ATX 12V Power Connector (12VCON1)                        |

| 3   | Micro-Fit Power Connector (ATX4PIN1)                     |

| 4   | ATX 12V Power Connector (12VCON2)                        |

| 5   | Chassis Intrusion Header (CASEOPEN1)                     |

| 6   | ATX 12V Power Connector (12VCON3)                        |

| 7   | System Fan Connector (FAN4)                              |

| 8   | Mini Cool Edge IO Connector (MCIO19)                     |

| 9   | Mini Cool Edge IO Connector (MCIO20)                     |

| 10  | 3 x 288-pin DDR5 DIMM Slots (DDR5_N1, DDR5_P1, DDR5_R1)* |

| 11  | 3 x 288-pin DDR5 DIMM Slots (DDR5_M1, DDR5_O1, DDR5_Q1)* |

| 12  | Mini Cool Edge IO Connector (MCIO17)                     |

| 13  | Mini Cool Edge IO Connector (MCIO18)                     |

| 14  | Mini Cool Edge IO Connector (MCIO15)                     |

| 15  | Mini Cool Edge IO Connector (MCIO16)                     |

| 16  | Mini Cool Edge IO Connector (MCIO13)                     |

| 17  | AMD Socket SP5 (SM-LGA-6096) (CPU1)                      |

| 18  | Mini Cool Edge IO Connector (MCIO14)                     |

| 19  | 3 x 288-pin DDR5 DIMM Slots (DDR5_S1, DDR5_U1, DDR5_W1)* |

| 20  | Mini Cool Edge IO Connector (MCIO11)                     |

| 21  | 3 x 288-pin DDR5 DIMM Slots (DDR5_T1, DDR5_V1, DDR5_X1)* |

| 22  | Mini Cool Edge IO Connector (MCIO12)                     |

| 23  | Thumbscrew                                               |

| 24  | Mini Cool Edge IO Connector (MCIO7)                      |

| 25  | 3 x 288-pin DDR5 DIMM Slots (DDR5_B1, DDR5_D1, DDR5_F1)* |

| 26  | Mini Cool Edge IO Connector (MCIO8)                      |

| 27  | 3 x 288-pin DDR5 DIMM Slots (DDR5_A1, DDR5_C1, DDR5_E1)* |

| 28  | Mini Cool Edge IO Connector (MCIO5)                      |

| 29  | Mini Cool Edge IO Connector (MCIO6)                      |

| 30  | AMD Socket SP5 (SM-LGA-6096) (CPU0)                      |

| 31  | Mini Cool Edge IO Connector (MCIO3)                      |

| 32  | 3 x 288-pin DDR5 DIMM Slots (DDR5_G1, DDR5_I1, DDR5_K1)* |

| 33  | Mini Cool Edge IO Connector (MCIO4)                      |

| 34  | Mini Cool Edge IO Connector (MCIO1)                      |

| No. | Description                                              |

|-----|----------------------------------------------------------|

| 35  | Mini Cool Edge IO Connector (MCIO2)                      |

| 36  | 3 x 288-pin DDR5 DIMM Slots (DDR5_H1, DDR5_J1, DDR5_L1)* |

| 37  | Mini Cool Edge IO Connector (MCIO10)                     |

| 38  | Mini Cool Edge IO Connector (MCIO9)                      |

| 39  | System Fan Connector (FAN3)                              |

| 40  | ATX 12V Power Connector (12VCON6)                        |

| 41  | ATX 12V Power Connector (12VCON5)                        |

| 42  | USB 3.2 Gen1 Header (USB3_5_6)                           |

| 43  | ATX 12V Power Connector (12VCON4)                        |

| 44  | System Power Connector (BP_PWR1)                         |

| 45  | SATA SGPIO Connector (SATA_SGPIO1)                       |

| 46  | System Panel Header (PANEL1)                             |

| 47  | Non Maskable Interrupt Button (NMI_BTN1)                 |

| 48  | Auxiliary Panel Header (AUX_PANEL1)                      |

| 49  | Liquid Crystal Module Header (LCM1)                      |

| 50  | Rear Panel LAN LED (RL_LED)                              |

| 51  | SATA SGPIO Connector (SATA_SGPIO3)                       |

| 52  | IPMI LAN LED Header (IPMI_LED1)                          |

| 53  | System Fan Connector (FAN1)                              |

| 54  | SATA SGPIO Connector (SATA_SGPIO4)                       |

| 55  | Clear CMOS Pad (CLRMOS1)                                 |

| 56  | System Fan Connector (FAN2)                              |

| 57  | SATA SGPIO Connector (SATA_SGPIO2)                       |

| 58  | Backplane PCI Express Hot-Plug Connector (CPU_HSBP1)     |

| 59  | Intelligent Platform Management Bus Header (IPMB1)       |

| 60  | SATA SGPIO Connector (SATA_SGPIO6)                       |

| 61  | PWM Configuration Header (PWM_CFG1)                      |

| 62  | SATA SGPIO Connector (SATA_SGPIO5)                       |

| 63  | PCIE Signal Source Selection Jumper (PCIE_BCM_SEL1)      |

| 64  | M.2 Socket (M2_1) (Type 2280/22110)                      |

| 65  | M.2 Socket (M2_2) (Type 2280/22110)                      |

| 66  | SPI TPM Header (TPM_BIOS_PH1)                            |

| 67  | NCSI Mode Jumper (NCSI_SEL1)                             |

| 68  | UID Button Header (UID_HD1)                              |

| No. | Description                    |

|-----|--------------------------------|

| 69  | NCSI Header (NCSI1)            |

| 70  | Front VGA Header (FRNT_VGA1)   |

| 71  | COM Port Header (COM1)         |

| 72  | USB 3.2 Gen1 Header (USB3_7_8) |

| 73  | BMC SMBus Header (BMC_SMB4)    |

| 74  | BMC SMBus Header (BMC_SMB3)    |

| 75  | System Fan Connector (FAN5)    |

| 76  | BMC SMBus Header (BMC_SMB2)    |

| 77  | System Fan Connector (FAN6)    |

| 78  | BMC SMBus Header (BMC_SMB1)    |

<sup>\*</sup> For DIMM installation and configuration instructions, please see p.20 (Installation of Memory Modules (DIMM)) for more details.

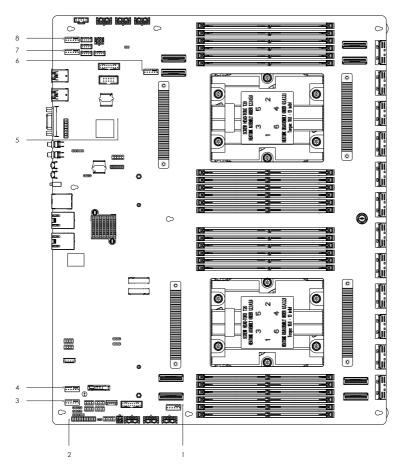

#### 1.5 Onboard LED Indicators

| No. | Item     | Status | Description       |

|-----|----------|--------|-------------------|

| 1   | LED_FAN3 | Red    | FAN3 failed       |

| 2   | SB_PWR1  | Green  | STB PWR ready     |

| 3   | LED_FAN1 | Red    | FAN1 failed       |

| 4   | LED_FAN2 | Red    | FAN2 failed       |

| 5   | BMC_LED1 | Green  | BMC heartbeat LED |

| 6   | LED_FAN4 | Red    | FAN4 failed       |

| 7   | LED_FAN5 | Red    | FAN5 failed       |

| 8   | LED_FAN6 | Red    | FAN6 failed       |

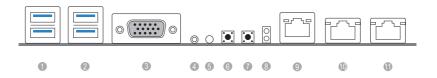

#### 1.6 I/O Panel

| No. | Description                   | No. | Description                            |

|-----|-------------------------------|-----|----------------------------------------|

| 1   | USB 3.2 Gen1 Ports (USB3_1_2) | 7   | NMI Button (NMI_BTN)                   |

| 2   | USB 3.2 Gen1 Ports (USB3_3_4) | 8   | HDD/System Fault LED (HDD_SYS_LED)     |

| 3   | VGA Header (VGA1)             | 9   | IPMI LAN Header (IPMI_LAN1)*           |

| 4   | UID Switch (UID1)             | 10  | 1G LAN RJ-45 Port (LAN1, shared NIC)** |

| 5   | Power Switch/LED (PWR_BTN1)   | 11  | 1G LAN RJ-45 Port (LAN2)**             |

| 6   | Reset Button (RST_BTN)        |     |                                        |

#### **LAN Port LED Indications**

\*There is an LED on each side of IPMI LAN port. Please refer to the table below for the LAN port LED indications.

#### **IPMI LAN Port LED Indications**

| Activity / Link LE | D             | Speed LED |                         |  |  |  |  |

|--------------------|---------------|-----------|-------------------------|--|--|--|--|

| Status             | Description   | Status    | Description             |  |  |  |  |

| Off                | No Link       | Off       | 10Mbps connection or no |  |  |  |  |

|                    |               |           | link                    |  |  |  |  |

| Blinking Yellow    | Data Activity | Orange    | 100Mbps connection      |  |  |  |  |

| On Link            |               | Green     | 1Gbps connection        |  |  |  |  |

English

\*\*There is an LED on each side of 1G LAN port. Please refer to the table below for the LAN port LED indications.

#### 1G LAN Port (LAN1, LAN2) LED Indications

| Activity / Link LE | D             | Speed LED |                      |  |  |  |  |

|--------------------|---------------|-----------|----------------------|--|--|--|--|

| Status             | Description   | Status    | Description          |  |  |  |  |

| Off                | No Link       | Off       | 10Mbps connection or |  |  |  |  |

|                    |               |           | no link              |  |  |  |  |

| Blinking Yellow    | Data Activity | Orange    | 100Mbps connection   |  |  |  |  |

| On                 | Link          | Green     | 1Gbps connection     |  |  |  |  |

#### **HDD/System Fault LED Indications**

| HDD LED |              | SYS FAULT LED |              |  |  |  |  |

|---------|--------------|---------------|--------------|--|--|--|--|

| Status  | Description  | Status        | Description  |  |  |  |  |

| Off     | HDD inactive | Off           | Normal       |  |  |  |  |

| Green   | HDD active   | RED           | System Fault |  |  |  |  |

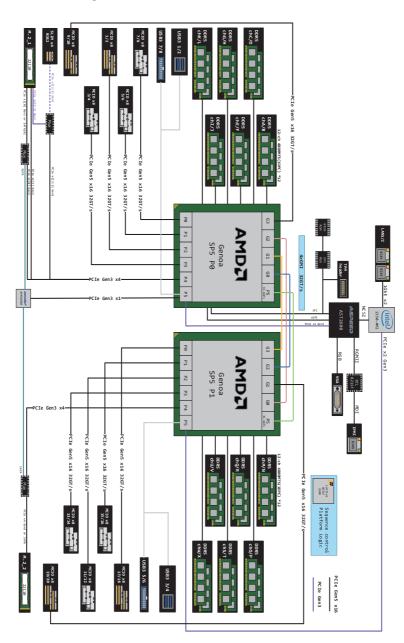

## 1.7 Block Diagram

## **Chapter 2 Installation**

This is a Proprietary form factor (18.93" x13.78") motherboard. Before installing the motherboard, study the configuration of the chassis to ensure that the motherboard fits into it.

Make sure to unplug the power cord before installing or removing the motherboard. Failure to do so may cause physical injuries and motherboard damages.

#### 2.1 Screw Holes

Place screws into the holes indicated by circles to secure the motherboard to the chassis.

Do not over-tighten the screws! Doing so may damage the motherboard.

#### 2.2 Pre-installation Precautions

Take note of the following precautions before installing motherboard components or change any motherboard settings.

- 1. Unplug the power cord from the wall socket before touching any components.

- To avoid damaging the motherboard's components due to static electricity, NEVER place the motherboard directly on the carpet or the like. Also remember to use a grounded wrist strap or touch a safety grounded object before handling the components

- 3. Hold components by the edges and do not touch the ICs.

- Whenever uninstall any component, place it on a grounded anti-static pad or in the bag that comes with the component.

- When placing screws into the screw holes to secure the motherboard to the chassis, please do not over-tighten the screws! Doing so may damage the motherboard.

Before installing or removing any component, ensure that the power is switched off or the power cord is detached from the power supply. Failure to do so may cause severe damage to the motherboard, peripherals, and/or components.

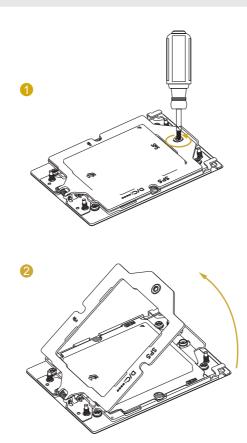

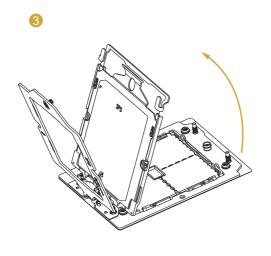

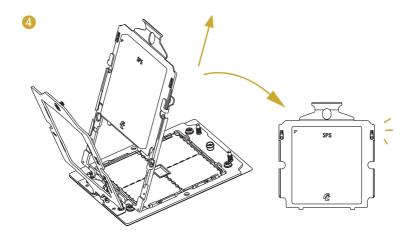

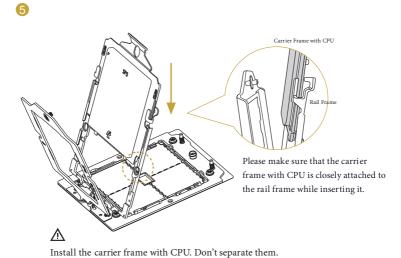

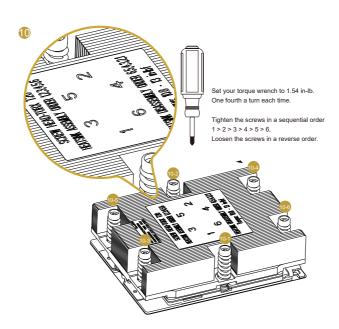

#### 2.3 Installing the CPU

- Before inserting the CPU into the socket, please check if the PnP cap is on the socket, if the CPU surface is unclean, or if there are any bent pins in the socket. Do not force to insert the CPU into the socket if above situation is found. Otherwise, the CPU will be seriously damaged.

- 2. Unplug all power cables before installing the CPU.

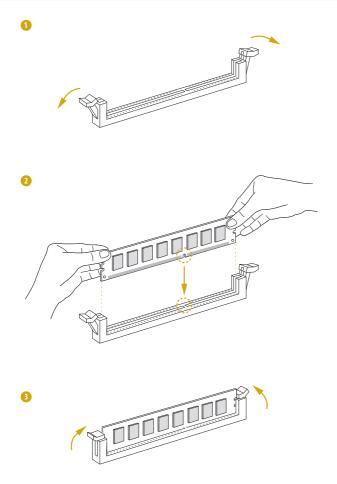

#### 2.4 Installation of Memory Modules (DIMM)

This motherboard provides twenty-four 288-pin DDR5 (Double Data Rate 5) DIMM slots in two groups, and supports Single Channel Memory Technology.

| CPU1                        | CPU0                        |

|-----------------------------|-----------------------------|

| DDR5_M1, N1, O1, P1, Q1, R1 | DDR5_A1, B1, C1, D1, E1, F1 |

| DDR5_S1, T1, U1, V1, W1, X1 | DDR5_G1, H1, I1, J1, K1, L1 |

- It is not allowed to install a DDR, DDR2, DDR3 or DDR4 memory module into a DDR5 slot; otherwise, this motherboard and DIMM may be damaged.

- For Single channel configuration, it always needs to install identical (the same brand, speed, size and chip-type) DDR5 DIMMs.

## Recommended Memory Configurations

|                                 |               | X      | >  |     |     |    |    |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

|---------------------------------|---------------|--------|----|-----|-----|----|----|-----|----|-----|----|-----|----|-----|----|-----|----|----|----|-----|----|-----|

|                                 | CPU1          | W1     | >  |     | >   |    | >  |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

|                                 |               | N      | Λ  |     | >   |    |    |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

|                                 |               | U      | >  |     | >   |    | >  |     | >  |     |    |     | >  |     |    |     |    |    |    |     |    |     |

|                                 |               | F      | Λ  |     | >   |    | >  |     | >  |     |    |     |    |     |    |     |    |    |    |     |    |     |

|                                 |               | S1     | Λ  |     | Λ   |    | >  |     | >  |     |    |     | >  |     |    |     | >  |    |    |     |    |     |

|                                 |               | R1     | Λ  |     |     |    |    |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

|                                 |               | 01     | Λ  |     | >   |    | >  |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

| els                             |               | P1     | Λ  |     | >   |    |    |     |    |     |    |     |    |     |    |     |    |    |    |     |    |     |

| hann                            |               | 01     | Λ  |     | >   |    | >  |     | >  |     |    |     | >  |     |    |     |    |    |    |     |    |     |

| lory C                          |               | N<br>N | Λ  |     | >   |    | >  |     | >  |     |    |     |    |     |    |     |    |    |    |     |    |     |

| Mem                             |               | M1     | Λ  |     | >   |    | >  |     | >  |     |    |     | >  |     |    |     | >  |    | >  |     |    |     |

| AMD Recommended Memory Channels |               | 11     | Λ  |     |     |    |    |     |    | >   |    |     |    |     |    |     |    |    |    |     |    |     |

| omme                            |               | K      | ^  |     | >   |    | >  |     |    | >   |    | >   |    | >   |    |     |    |    |    |     |    |     |

| ) Rec                           |               | 7      | Λ  |     | >   |    |    |     |    | >   |    | >   |    |     |    |     |    |    |    |     |    |     |

| AMI                             |               | 1      | Λ  |     | >   |    | >  |     | >  | >   |    | >   | >  | >   |    | >   |    | >  |    |     |    |     |

|                                 |               | Ŧ      | Λ  |     | >   |    | >  |     | >  | >   |    | >   |    | >   |    | >   |    |    |    |     |    |     |

|                                 |               | G1     | Λ  |     | >   |    | >  |     | >  | >   |    | >   | >  | >   |    | >   | >  | >  |    | >   |    |     |

|                                 | 9             | E      | Λ  |     |     |    |    |     |    | >   |    |     |    |     |    |     |    |    |    |     |    |     |

|                                 | CPU0          | 10     | ^  |     | >   |    | >  |     |    | >   |    | >   |    | >   |    |     |    |    |    |     |    |     |

|                                 |               | D1     | ^  |     | >   |    |    |     |    | >   |    | >   |    |     |    |     |    |    |    |     |    |     |

|                                 |               | Cl     | Λ  |     | >   |    | >  |     | >  | >   |    | >   | >  | >   |    | >   |    | >  |    |     |    |     |

|                                 |               | B1     | ^  |     | >   |    | >  |     | >  | >   |    | >   |    | >   |    | >   |    |    |    |     |    |     |

|                                 |               | A1     | Λ  |     | >   |    | >  |     | >  | >   |    | >   | >  | >   |    | >   | >  | >  | >  | >   |    | >   |

|                                 | Number of CPU |        | 2P | 11P | 2P  | 1P | 2P | 11P | 2P | 1P | 2P | 11P | 2P | 11P |

| Number of                       |               |        | 20 |     | 707 | 16 |    | 12  |    | ç   | 2  | d   | 8  |     | 9  |     | 4  |    | 2  |     | -  |     |

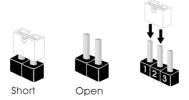

#### 2.5 Jumper Setup

The illustration shows how jumpers are setup. When the jumper cap is placed on the pins, the jumper is "Short". If no jumper cap is placed on the pins, the jumper is "Open". The illustration shows a 3-pin jumper whose pin1 and pin2 are "Short" when a jumper cap is placed on these 2 pins.

NCSI Mode Jumper (3-pin NCSI\_SEL1) (see p.6, No. 67)

NCSI to I350 (Default)

NCSI to NCSI Header (NCSI1)

PCIE Signal Source Selection Jumper (3-pin PCIE\_BCM\_SEL1) (see p.6, No. 63)

$RDS2 + M.2_1 (x2)$

M.2\_1 (x4) (Default)

RDS2 shares singal source with M.2\_1:

1. RDS2 is PCIe3.0 x2 when M2\_1 supports only PCIe3.0 x2 or SATA 6Gb/s

2. RDS2 is no function when M2\_1 supports PCIe3.0 x4 or SATA 6Gb/s

#### 2.6 Onboard Headers and Connectors

Onboard headers and connectors are NOT jumpers. Do NOT place jumper caps over these headers and connectors. Placing jumper caps over the headers and connectors will cause permanent damage to the motherboard.

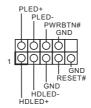

System Panel Header (9-pin PANEL1) (see p.6, No.46)

Connect the power switch, reset switch and system status indicator on the chassis to this header according to the pin assignments. Particularly note the positive and negative pins before connecting the cables.

#### PWRBTN (Power Switch):

Connect to the power switch on the chassis front panel. It may configure the way to turn off the system using the power switch.

#### RESET (Reset Switch):

Connect to the reset switch on the chassis front panel. Press the reset switch to restart the computer if the computer freezes and fails to perform a normal restart.

#### PLED (System Power LED):

Connect to the power status indicator on the chassis front panel. The LED is on when the system is operating. The LED is off when the system is in S4 sleep state or powered off (S5).

#### HDLED (Hard Drive Activity LED):

Connect to the hard drive activity LED on the chassis front panel. The LED is on when the hard drive is reading or writing data.

The front panel design may differ by chassis. A front panel module mainly consists of power switch, reset switch, power LED, hard drive activity LED, speaker and etc. When connecting the chassis front panel module to this header, make sure the wire assignments and the pin assignments are matched correctly.

Serial Port Header (9-pin COM1) (see p.6, No. 71)

This COM header supports a serial port module.

Enalish

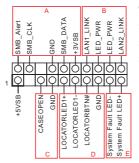

Auxiliary Panel Connector (18-pin AUX\_PANEL1) (see p.6, No. 48)

This header supports multiple functions on the front panel, including front panel SMB, internet status indicator.

A. Front panel SMBus connecting pin (6-1 pin FPSMB)

This header allows user to connect SMBus (System Management Bus) equipment. It can be used for communication between peripheral equipment in the system, which has slower transmission rates, and power management equipment.

B. Internet status indicator (2-pin LAN1\_LED, LAN2\_LED)

These two 2-pin headers allow user to use the Gigabit internet indicator cable to connect to the LAN status indicator. When this indicator flickers, it means that the internet is properly connected.

#### C. Chassis intrusion pin (2-pin CHASSIS)

This header is provided for host computer chassis with chassis intrusion detection designs. In addition, it must also work with external detection equipment, such as a chassis intrusion detection sensor or a microswitch. When this function is activated, if any chassis component movement occurs, the sensor will immediately detect it and send a signal to this header, and the system will then record this chassis intrusion event. The default setting is set to the CASEOPEN and GND pin; this function is off.

D. Locator LED (4-pin LOCATOR)

This header is for the locator switch and LED on the front panel.

E. System Fault LED (2-pin LOCATOR)

This header is for the Fault LED on the system.

Non Maskable Interrupt Button Header (2-pin NMI\_BTN1) (see p.6, No. 47)

Please connect a NMI device to this header.

USB 3.2 Gen1 Headers (19-pin USB3\_5\_6) (see p.6, No. 42) (19-pin USB3\_7\_8) (see p.6, No. 72)

Besides four default USB 3.2 Gen1 ports on the I/O panel, there are two USB 3.2 Gen1 headers on this motherboard. Each USB 3.2 Gen1 header can support two USB 3.2 Gen1 ports.

SPI TPM Header (13-pin TPM\_BIOS\_PH1) (see p.6, No. 66)

This connector supports SPI Trusted Platform Module (TPM) system, which can securely store keys, digital certificates, passwords, and data. A TPM system also helps enhance network security, protects digital identities, and ensures platform integrity.

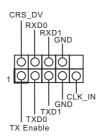

Front VGA Header (15-pin FRNT\_VGA1) (see p.6, No. 70)

DDC\_CLK Please connect either end of H\_SYNC the VGA cable to this VGA header

NCSI Header (9-pin NCSI1) (see p.6, No. 69)

The onboard NCSI header is used for external connections.

Serial General Purpose Input/Output Headers (7-pin SATA\_SGPIO1) (see p.6, No. 45) (7-pin SATA\_SGPIO2) (see p.6, No. 57) (7-pin SATA\_SGPIO3) (see p.6, No. 51) (7-pin SATA\_SGPIO4) (see p.6, No. 54) (7-pin SATA\_SGPIO5) (see p.6, No. 62) (7-pin SATA\_SGPIO6) (see p.6, No. 60)

These headers support Serial Link interface for onboard SATA connections.

PWM Configuration Header (3-pin PWM\_CFG1) (see p.6, No. 61)

This header is used for PWM configurations.

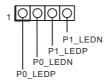

IPMI LAN LED Header (4-pin IPMI\_LED1) (see p.6, No. 52)

This header is used to connect to the LED indicators on the chassis.

Rear Panel LAN LED (4-pin RL\_LED) (see p.6, No. 50)

This header is used for extended LAN LED on the rear panel of a server system.

Chassis Intrusion Header (2-pin CASEOPEN1) (see p.6, No. 5)

This motherboard supports CASE OPEN detection feature that detects if the chassis cover has been removed. This feature requires a chassis with chassis intrusion detection design. Liquid Crystal Module Header (4-pin LCM1) (see p.6, No. 49)

This header is used for extended Liquid Crystal Module(LCM) on the front panel of a server system.

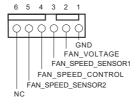

System Fan Connectors (6-pin FAN1) (see p.6, No. 53) (6-pin FAN2) (see p.6, No. 56) (6-pin FAN3) (see p.6, No. 39) (6-pin FAN4) (see p.6, No. 7) (6-pin FAN5)

(see p.6, No. 75) (6-pin FAN6) (see p.6, No. 77)

ATX 12V Power

Please connect fan cables to the fan connectors and match the black wire to the ground pin. All fans support Fan Control.

Connectors (8-pin 12VCON1) (see p.6, No. 2) (8-pin 12VCON2) (see p.6, No. 4) (8-pin 12VCON3) (see p.6, No. 6) (8-pin 12VCON4) (see p.6, No. 43) (8-pin 12VCON5) (see p.6, No. 41) (8-pin 12VCON6) (see p.6, No. 40)

This motherboard provides six ATX power connectors.

System Power Connector (2-pin BP\_PWR1)

(see p.6, No. 44)

This motherboard provides one +5V power connector for system configuration.

Enalish

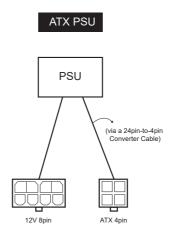

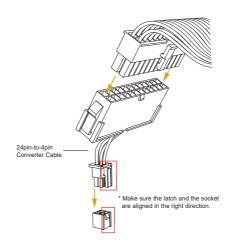

Micro-Fit ATX 4Pin Power Connector (4-pin ATX4PIN1 (ATX 24pin-to-4pin)) (see p.6, No. 3)

The motherboard provides one 4-pin power/signal connector which is a required input for ATX power source. When using ATX power, it is necessary to use a 24pin-to-4pin power cable to connect between the 24pin power connector of PSU and the 12VCON1~6 connectors on the motherboard for power supply and signal communication

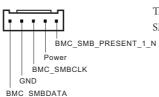

BMC SMB Headers (5-pin BMC\_SMB1) (see p.6, No. 78) (5-pin BMC\_SMB2) (see p.6, No. 76) (5-pin BMC\_SMB3) (see p.6, No. 74) (5-pin BMC\_SMB4) (see p.6, No. 73)

These headers are used for the SMBUS devices.

Intelligent Platform Management Bus header (4-pin IPMB1) (see p.6, No. 59)

This 4-pin connector is used to provide a cabled baseboard or front panel connection for value added features and 3rd-party add-in cards, such as Emergency Management cards, that provide management features using the IPMB.

LOCATORLED-UID Header This 4-pin header is used for LOCATORBTN# the Unit Identification LED (4-pin UID\_HD) +5VSB GND and switch functions. (see p.6, No. 68) RRXD1 COM Port Header This COM header supports a DDTR#1 (9-pin COM1) DDSR#1 serial port module. CCTS# (see p.6, No. 71) RRI#1 RRTS#1 GND TTXD1 DDCD#1 PSU SMBus PSU SMBus monitors the SMBCLK +3VSB (PSU\_SMB1) status of the power supply, fan (see p.6, No. 1) and system temperature. **SMBDATA** GND This header is used for the hot Backplane PCI Express CPU HP SCL Hot-Plug Connector plug feature of HDDs on the CPU\_HP\_SDA (5-pin CPU\_ HSBP1) backplane. P0 HP ALERT L GND (see p.6, No. 58) 1 Clear CMOS Pad This allows user to clear (CLRMOS1) the data in CMOS. To clear (see p.6, No. 55) CMOS, take out the CMOS battery and short the Clear

CMOS Pad.

MCIO Connectors

(MCIO1)

(see p.6, No. 34)

(MCIO2)

(see p.6, No. 35)

(MCIO9)

(see p.6, No. 38)

(MCIO10)

(see p.6, No. 37)

(MCIO17)

(see p.6, No. 12)

(MCIO18)

(see p.6, No. 13)

(MCIO19)

(see p.6, No. 8)

(MCIO20)

(see p.6, No. 9)

### Right Angle

(MCIO3)

(see p.6, No. 31)

(MCIO4)

(see p.6, No. 33)

(MCIO5)

(see p.6, No. 28)

(MCIO6)

(see p.6, No. 29)

(MCIO7)

(see p.6, No. 24)

(MCIO8)

(see p.6, No. 26)

(MCIO11)

(see p.6, No. 20)

(MCIO12)

(see p.6, No. 22)

(MCIO13)

(see p.6, No. 16)

(MCIO14)

(see p.6, No. 18)

(MCIO15)

(see p.6, No. 14)

(MCIO16)

(see p.6, No. 15)

# These connectors are used for the PCIE or SATA devices.

\* MCIO9, 10 support PCIe only while installing 2 processors

## MCIO1 Pin Definition (CPU0 P2 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| A3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | B5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | B7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP1      | B32 | TX_DP1       |

| A33 | RX_DN1      | B33 | TX_DN1       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP0      | B35 | TX_DP0       |

| A36 | RX_DN0      | B36 | TX_DN0       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

## MCIO2 Pin Definition (CPU0 P2 [15:8])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP15     | B2  | TX_DP15      |

| A3  | RX_DN15     | В3  | TX_DN15      |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP14     | B5  | TX_DP14      |

| A6  | RX_DN14     | В6  | TX_DN14      |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP13     | B14 | TX_DP13      |

| A15 | RX_DN13     | B15 | TX_DN13      |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP12     | B17 | TX_DP12      |

| A18 | RX_DN12     | B18 | TX_DN12      |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP11     | B20 | TX_DP11      |

| A21 | RX_DN11     | B21 | TX_DN11      |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP10     | B23 | TX_DP10      |

| A24 | RX_DN10     | B24 | TX_DN10      |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP9      | B32 | TX_DP9       |

| A33 | RX_DN9      | B33 | TX_DN9       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP8      | B35 | TX_DP8       |

| A36 | RX_DN8      | B36 | TX_DN8       |

| A37 | GND         | B37 | GND          |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

# MCIO3 Pin Definition (CPU0 P3 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| A3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | B5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP1      | B32 | TX_DP1       |

| A33 | RX_DN1      | B33 | TX_DN1       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP0      | B35 | TX_DP0       |

| A36 | RX_DN0      | B36 | TX_DN0       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

## MCIO4 Pin Definition (CPU0 P3 [15:8])

|     | - C 1 111   |     | D ( ) 111    |

|-----|-------------|-----|--------------|

| Pin | Defeinition | Pin | Defeinition  |

| A1  | GND         | B1  | GND          |

| A2  | RX_DP15     | B2  | TX_DP15      |

| A3  | RX_DN15     | В3  | TX_DN15      |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP14     | B5  | TX_DP14      |

| A6  | RX_DN14     | В6  | TX_DN14      |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP13     | B14 | TX_DP13      |

| A15 | RX_DN13     | B15 | TX_DN13      |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP12     | B17 | TX_DP12      |

| A18 | RX_DN12     | B18 | TX_DN12      |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP11     | B20 | TX_DP11      |

| A21 | RX_DN11     | B21 | TX_DN11      |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP10     | B23 | TX_DP10      |

| A24 | RX_DN10     | B24 | TX_DN10      |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP9      | B32 | TX_DP9       |

| A33 | RX_DN9      | B33 | TX_DN9       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP8      | B35 | TX_DP8       |

| A36 | RX_DN8      | B36 | TX_DN8       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

# MCIO5 Pin Definition (CPU0 P1 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| A3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | B5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP1      | B32 | TX_DP1       |

| A33 | RX_DN1      | B33 | TX_DN1       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP0      | B35 | TX_DP0       |

| A36 | RX_DN0      | B36 | TX_DN0       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

## MCIO6 Pin Definition (CPU0 P1 [15:8])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP15     | B2  | TX_DP15      |

| A3  | RX_DN15     | В3  | TX_DN15      |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP14     | B5  | TX_DP14      |

| A6  | RX_DN14     | В6  | TX_DN14      |

| A7  | GND         | B7  | GND          |

| A8  | BP_TYPE     | B8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP13     | B14 | TX_DP13      |

| A15 | RX_DN13     | B15 | TX_DN13      |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP12     | B17 | TX_DP12      |

| A18 | RX_DN12     | B18 | TX_DN12      |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP11     | B20 | TX_DP11      |

| A21 | RX_DN11     | B21 | TX_DN11      |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP10     | B23 | TX_DP10      |

| A24 | RX_DN10     | B24 | TX_DN10      |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP9      | B32 | TX_DP9       |

| A33 | RX_DN9      | B33 | TX_DN9       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP8      | B35 | TX_DP8       |

| A36 | RX_DN8      | B36 | TX_DN8       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

# MCIO7 Pin Definition (CPU0 P0 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| А3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | В5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP1      | B32 | TX_DP1       |

| A33 | RX_DN1      | B33 | TX_DN1       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP0      | B35 | TX_DP0       |

| A36 | RX_DN0      | B36 | TX_DN0       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

## MCIO8 Pin Definition (CPU0 P0 [15:8])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP15     | B2  | TX_DP15      |

| A3  | RX_DN15     | В3  | TX_DN15      |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP14     | B5  | TX_DP14      |

| A6  | RX_DN14     | В6  | TX_DN14      |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | B8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP13     | B14 | TX_DP13      |

| A15 | RX_DN13     | B15 | TX_DN13      |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP12     | B17 | TX_DP12      |

| A18 | RX_DN12     | B18 | TX_DN12      |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP11     | B20 | TX_DP11      |

| A21 | RX_DN11     | B21 | TX_DN11      |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP10     | B23 | TX_DP10      |

| A24 | RX_DN10     | B24 | TX_DN10      |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP9      | B32 | TX_DP9       |

| A33 | RX_DN9      | B33 | TX_DN9       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP8      | B35 | TX_DP8       |

| A36 | RX_DN8      | B36 | TX_DN8       |

| A37 | GND         | B37 | GND          |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

# MCIO9 Pin Definition (CPU0 G3 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| A3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | B5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP1      | B32 | TX_DP1       |

| A33 | RX_DN1      | B33 | TX_DN1       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP0      | B35 | TX_DP0       |

| A36 | RX_DN0      | B36 | TX_DN0       |

| A37 | GND         | B37 | GND          |

|     |             |     |              |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

## MCIO10 Pin Definition (CPU0 G3 [15:8])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP15     | B2  | TX_DP15      |

| A3  | RX_DN15     | В3  | TX_DN15      |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP14     | B5  | TX_DP14      |

| A6  | RX_DN14     | В6  | TX_DN14      |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | B8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP13     | B14 | TX_DP13      |

| A15 | RX_DN13     | B15 | TX_DN13      |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP12     | B17 | TX_DP12      |

| A18 | RX_DN12     | B18 | TX_DN12      |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP11     | B20 | TX_DP11      |

| A21 | RX_DN11     | B21 | TX_DN11      |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP10     | B23 | TX_DP10      |

| A24 | RX_DN10     | B24 | TX_DN10      |

| A25 | GND         | B25 | GND          |

| A26 | BP_TYPE     | B26 | SCL2         |

| A27 | WAKE#       | B27 | SDA2         |

| A28 | GND         | B28 | GND          |

| A29 | DP2         | B29 | PERST_BUF2_N |

| A30 | DN2         | B30 | PRSNT_N      |

| A31 | GND         | B31 | GND          |

| A32 | RX_DP9      | B32 | TX_DP9       |

| A33 | RX_DN9      | B33 | TX_DN9       |

| A34 | GND         | B34 | GND          |

| A35 | RX_DP8      | B35 | TX_DP8       |

| A36 | RX_DN8      | B36 | TX_DN8       |

| A37 | GND         | B37 | GND          |

| 75  | NP_NC_1     | 76  | NP_NC_2      |

| 77  | PGND_1      | 78  | PGND_3       |

| 79  | PGND_2      | 80  | PGND_4       |

# MCIO11 Pin Definition (CPU1 P2 [7:0])

| Pin | Defeinition | Pin | Defeinition  |

|-----|-------------|-----|--------------|

| A1  | GND         | B1  | GND          |

| A2  | RX_DP7      | B2  | TX_DP7       |

| A3  | RX_DN7      | В3  | TX_DN7       |

| A4  | GND         | B4  | GND          |

| A5  | RX_DP6      | B5  | TX_DP6       |

| A6  | RX_DN6      | В6  | TX_DN6       |

| A7  | GND         | В7  | GND          |

| A8  | BP_TYPE     | В8  | SCL1         |

| A9  | WAKE#       | В9  | SDA1         |

| A10 | GND         | B10 | GND          |

| A11 | DP1         | B11 | PERST_BUF1_N |

| A12 | DN1         | B12 | PRSNT_N      |

| A13 | GND         | B13 | GND          |

| A14 | RX_DP5      | B14 | TX_DP5       |

| A15 | RX_DN5      | B15 | TX_DN5       |

| A16 | GND         | B16 | GND          |

| A17 | RX_DP4      | B17 | TX_DP4       |

| A18 | RX_DN4      | B18 | TX_DN4       |

| A19 | GND         | B19 | GND          |

| A20 | RX_DP3      | B20 | TX_DP3       |

| A21 | RX_DN3      | B21 | TX_DN3       |

| A22 | GND         | B22 | GND          |

| A23 | RX_DP2      | B23 | TX_DP2       |

| A24 | RX_DN2      | B24 | TX_DN2       |